FET

TRANSISTORI AD EFFETTO DI CAMPO (FIELD EFFECT TRANSISTOR)

I FET sono dei generatori di corrente controllati in tensione.

Prendiamo 3 terminali e posizioniamoli come in fig.1.

Il terminale 3 è in comune agli altri due.

All' ingresso abbiamo la tensione v1 in uscita la corrente

i2 = gm v1 .

La corrente i2 è controllata dalla tensione v1.

Disegniamo la caratteristica di uscita ; notiamo che i2 dipende da v1 e non da v2 ( v1 è utilizzato come parametro) pertanto l'andamento di i2 in funzione di v2 è rappresentato da delle rette parallele all'asse v2 .

Se ora vogliamo trovare il punto di riposo del generatore di corrente lo dobbiamo inserire in un circuito ; per esempio inseriamo il generatore di corrente nel circuito costituito del generato Vcc e la resistenza di carico Rc (in rosso nella fig.1); possiamo scrivere :

v2 = Vcc- (Rc x i2 ) che rappresenta la retta di carico del circuito.

Sovrapponendo la retta di carico alla caratteristica di uscita

questa incontrerà l'asse delle ascisse nel punto v2 = Vcc e l'asse delle ordinate nel punto i2 = Vcc /Rc ; se ora scegliamo v1 = v11 la retta di carico intersecherà la retta i2 = gm v11 nel punto Q che rappresenta il punto di riposo cercato.

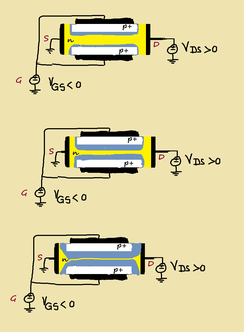

JFET

In fig.2 è disegnato un nJFET cioè un FET a canale n; esiste ma è poco usato il pJFET cioè il FET a canale p.

JFET è l'acronimo di Juncion gate Field Effect Transistor.

Affinchè questo marchingegno funzioni si pone il Source a massa , la tensione VGS < 0 e la tensione VDS positiva prossima allo zero .

In tal modo la giunzione PN risulta polarizzata inversamente.

Man mano che diminuisce VGS il canale n si restringe in modo costante ( ricordarsi che la tensione di D è di pochissimo diversa (superiore) a quella di S) lungo tutta la sua lunghezza , la resistenza del canale aumenta e la corrente fra D ed S diminuisce .

Quando la VGS raggiunge un valore di soglia pari a VP (negativa) chiamata tensione di pinch -off il canale scompare e la corrente cessa di circolare; siamo in zona di interdizione.

E' bene porre in evidenza che il JFET ha una struttura simmetrica , posso sostituire cioè il Source (sorgente) col Drain (pozzo) e nulla cambia; l'importante è che il Source sia a massa che il Drain abbia una tensione maggiore di zero e che il gate abbia una tensione minore di zero (ci stiamo riferendo ad un nJFET; per un pJFET, molto meno utilizzato, i segni evidentemente cambiano).

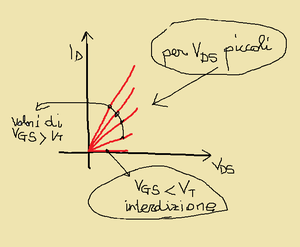

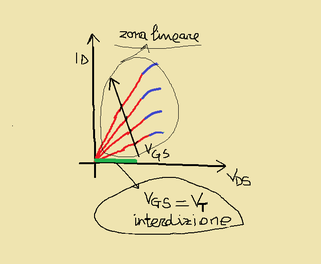

Vediamo in fig. 2b la caratteristica di uscita ID=f( VDS) con parametro VGS.

Per VGS = Vp siamo nella zona di interdizione e si ha

ID= 0, man mano che VGS aumenta di valore ( diventa meno negativa) l'andamento della corrente ID in funzione di VDS sarà rappresento da una retta la cui pendenza (ID/VDS ) aumenta all'aumentare di VGS.

Se aumenta la pendenza diminuisce la resistenza (VDS /ID ) del canale .

Possiamo dire in questo caso di essere in presenza di una resistenza controllata da tensione.

Per poer affermare che il dispositivo è un generatore di corrente controllato in tensione occore fare il seguente ragionamento:

Finora abbiamo ragionato supponendo la VDS molto piccola; vediamo ora cosa succede se la VDS cresce e la VGS si mantiene costante minore di zero e maggiore di VP ( VP< VGS<0).

In queste condizioni osserviamo che la tensione VGS risulta maggiore della tensione VGD.

Infatti se osserviamo la fig.2c possiamo scrivere:

VGD = VGS - VDS.

Ora poichè VDS è sempre positivo risulta VGS > VGD .

In queste condizioni ci sarà in corrispondenza del Source un maggior accumulo di cariche che non in corrispondenza del Drain; in altre parole possiamo affermare che il marchingegno è polarizzato inversamente in prossimità del drain più di quanto non lo sia in prossimità del sourse.

A questo punto il canale assumerà una forma triangolare come in fig.2b1 .

In particolare in fig.2b1 A) è rappresentato il caso in cui

VGD = VP ; in questo caso poiché VGD = VGS - VDS = VP risulta :

VDS = VGS - VP ; questa espressione rappresenta la condizione per cui il canale si annulla nel Drain.

Nelle fig.2b1 B) e C) è rappresentato il canale per VDS crescenti.

Osservando le fig.2b1 B) e C) ci rendiamo conto che il punto di strozzamento è arretrato fino al punto di pinch-off dove la tensione VGX = VP; allora possiamo scrivere VGX = VGS- VP .

Da questa espressione si nota che il punto X arretra pochissimo rispetto al Drain e che pertanto la resistenza del canale rimane costante .

Ciò porta ad una corrente ID che rimane costante all'aumentare di VDS .

In fig2d è indicato il completamento del grafico di fig.2b.

Il tratto in giallo rappresenta l'andamento della corrente dal momento in cui VGS diventa maggiore di VGD al momento in cui si ha VGD = VP.

il tratto presenta una concavità verso il basso che indica che la corrente sta aumentando più lentamente all'aumentare di VDS.

Raggiunto il punto di pinch-off la corrente in prima approssimazione non aumenta più mantenendosi costante.

In realtà un piccolo aumento si manifesta a causa del fatto che il canale un poco si accorcia.

Ora si può affermare di essere in presenza di un generatore di corrente controllato da tensione.

Un grafico interessante e quello che rappresenta le caratteristiche di trasferimento che rappresenta l'andamento della corrente ID al variare della VGS a VDS costante; il ragionamento vale per qualunque valore di VDS purchè ci si trovi in zona di saturazione ( vedi fig.2d).

L'andamento è parabolico e approssimativamente può essere descritto dalla formula :

ID = IDSS (1-VGS/VP)2 (1+λVDS)

il termine (1+λVDS), poichè λ è molto piccolo, diventa di pochissimo maggiore di 1 e tiene conto della modulazione della lunghezza del canale ( vedi linea azzurra di fig.2d).

λ è il fattore di modulazione della lunghezza del canale.

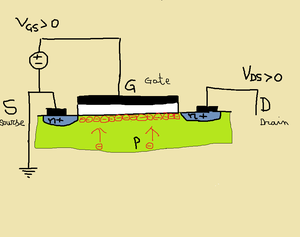

nMOSFET

In fig. 3 è disegnato un MOSFET a canale n ; il MOSFET può essere anche a canale p (pMOSFET) ; sia il MOSFET a canale n che quello a canale p sono utilizzati moltissimo.

MOS è l'acronimo di Metal Oxide Semiconductor.

Come si nota nella fig.3 il nMOSFET è costituito da due zone n molto drogate a contatto con una zona drogata p.

Fra le due zone n+ c'è un isolante costituito da ossido di Afnio che ormai ha sostituito l'ossido di silicio che era utilizzato fino alla fine del primo decennio di questo secolo .

Sull'isolante c'è il Gate.

Il Gate, l'isolante e la zona p formano un condensatore piano a facce parallele.

Nella configurazione di fig.3 , pur applicando una differenza di potenziale fra D e S il marchingegno non conduce.

Cosa devo fare perchè conduca?

Affinchè conduca ( o meglio , si predisponga il dispositivo per la conduzione) occorre intanto collegare a terra il Sourse, poi applicare una tensione VGS >0 fra Gate e Sourse ed applicare una tensione VDS >0 fra Drain e Sourse.

Cosa succede?

Succede che la tensione applicata fra Gate e Sourse , VGS >0 attira degli elettroni che come si nota in figura si adagiano a contatto con la superficie dell'isolante fino a formare un canale fra le due zone drogate n+.

Questo canale si forma gradualmete e solo al raggiungimento di una tensione VGS di soglia che chiamiamo VT possiamo dire che si sia formato completamente mettendo in contatto le due zone n+ .

A questo punto se applichiamo una tensione tra Drain e Sourse VDS > 0 anche piccolissima avrò un flusso di elettroni che dal Sourse (Sorgente) andranno a finire nel Drain (pozzo); la corrente evidentemente fluirà fra Drain e Sourse.

Nella fig.3b è rappresentata la caratteristica d'uscita, cioè l'andamento della ID in funzione della VDS utilizzando come parametro la VGS.

Per VGS < VT non si ha passaggio di corrente (interdizione: ID=0 ) per VGS > VT si è formato il canale n e pertanto circola corrente fra D ed S ; maggiore è VGS minore sarà la resistenza del canale maggiore sarà la corrente ID.

Quanto sopra vale per valori piccoli di VDS.

Cosa succede se manteniamo la VGS fissa ad un valore superiore a VT ed aumentiamo il valore della VDS? succede quanto riportato in fig. 3d.

Il canale assume la forma triangolare con lo spessore del canale più grande in corrispondenza del Sourse

Questo perché al crescere della VDS , la VGS cresce e la VGD diminuisce.

Evidenziando infatti che:

VGD = VGS - VDS (vedi fig.3c)

notiamo che al crescere di VDS (sempre positiva) VGS rimane sempre maggiore di VGD.

Con valori elevati di VDS ci saranno pertanto più cariche vicine ad Sourse che non al Drain.

Assumendo la forma di fig.3d il canale avrà un aumento della sua resistenza ; la caratteristica d'uscita diverrà pertanto come in fig.3e.

La parte azzurra indica una aumento più lento della corrente all'aumentare della VDS.

Con buona approssimazione possiamo scrivere che

l' espressione della ID in zona lineare é:

ID =β (2(VGS - VT)VDS - VDS2)

Se ora la tensione VDS continua ad aumentare si arriva al punto in cui il canale si strozza proprio in corrispondenza del Drain (fig.3f A)

La tensione in corrispondenza della quale questo avviene è : VGD = VT .

Ora , poichè VGD = VGS - VDS =VT, risulta :

VDS = VGS - VT (condizione necessaria perché il canale si annulli nel Drain).

Nelle fig.3f B) e C) è rappresentato il canale per VDS crescenti.

Osservando le fig.3f B) e C) ci rendiamo conto che il punto di strozzamento è arretrato fino al punto di pinch-off dove la tensione VGX = VT; allora possiamo scrivere VGX= VGS- VT .

Da questa espressione si nota che il punto X arretra pochissimo rispetto al Drain e che pertanto la resistenza del canale rimane costante .

Ciò porta ad una corrente ID che rimane costante all'aumentare di VDS .

In fig.3g è indicato il completamento del grafico di fig.3e.

Il tratto in giallo rappresenta l'andamento della corrente dal momento in cui VGS diventa maggiore di VGD al momento in cui si ha VGD = VT.

il tratto presenta una concavità verso il basso che indica che la corrente sta aumentando più lentamente all'aumentare di VDS.

Raggiunto il punto di pinch-off la corrente in prima approssimazione non aumenta più mantenendosi costante.

In realtà un piccolo aumento si manifesta a causa del fatto che il canale un poco si accorcia.

Siamo in presenza di un generatore di corrente controllato da tensione.

Un grafico interessante e quello che delle caratteristiche di trasferimento (fig.3h) ; esso rappresenta l'andamento della corrente ID al variare della VGS.

L'andamento in saturazione è parabolico e approssimativamente può essere descritto dalla formula :

ID = β (VGS - VT)2(1+λVDS)

Il il termine (1+λVDS), molto piccolo, tiene conto della modulazione della lunghezza del canale ( vedi linea azzurra di fig.3g).

β è una costante che tiene conto della geometria e delle caratteristiche del dispositivo.

λ è il fattore di modulazione della lunghezza del canale.

In fig 3h1 è spiegato il significato di β.

è un parametro usato nella progettazione . Di solito gli unici elementi che vanno variati sono L e W. gli altri elementi sono sempre uguali per tutti i MOSFET.

FET

ANALISI DI PICCOLO SEGNALE

Il ragionamento che andiamo a fare è del tutto generale e vale sia per i JFET che per MOSFET.

prendiamo in condiderazione un JFET come in fig.4 in configurazione a Sourse comune.

La ID è funzione di VGS e di VDS , cioè : ID = iD (VGS, VDS) .

In presenza del segnale alternato vs la corrente totale nel punto di riposo Q sarà : ID +id = ID (VGS + vGS , VDS+ vGS) .

A noi interessa studiare l'andamento della corrente in un intorno del punto Q e per farlo linearizziamo l'andamento della funzione che rappresenta la

corrente in modo da sostituirla con una retta (la tangente alla curva nel punto Q) .

Per fare questa linearizzazione utilizziamo lo sviluppo in serie di Taylor fermandoci al primo ordine.

Scriviamo quindi:

ID+id= iD (VGS, VDS) + (δ iD/δvGS) vGS + (δ iD/δvDS)vDS

le due derivate parziali sono calcolate in Q.

poichè ID= iD (VGS, VDS) l'espressione diventa:

id= (δ iD/δvGS) vGS + (δ iD/δvDS)vDS .

poniamo (δ iD/δvGS) = gm ( è una transconduttanza) e

(δ iD/δvDS) = go ( è una conduttanza).

L'espressione diventa: Id= gm vGS + govDS .

l'espressione dal punto di vista circuitale e rappresentata in fig.4a.

Per quanto riguarda la caratteristica di ingresso mettiamo in evidenza che nel JFET fra Gate e Sourse non passa corrente poiché la giunzione è polarizzata inversamente, (in realtà nel JFET passa la corrente di saturazione inversa che tuttavia è trascurabile) ; Nel Mosfet fra Gate e Sourse non passa nessuna corrente perchè i due terminale sono separati da un isolante (ossido di Afnio).

Possiamo dunque affermare in generale che nel FET IG=0

Nella realtà il circuito equivalente di fig.4a va modificato.

Esistono infatti delle capacita fra Gate e Sourse e fra Gate e Drain sia nel JFET che nel MOSFET come mostrato in fig.4b.

le capacità CGS e CGD nella zona lineare sono uguali fra loro mentre, in zona di saturazione risulta : CGS > CGD.

Con le due capacità il circuito equivalente diventa come in fig.4c.

Si conclude che il circuito equivalente di piccolo segnale riportato in fig.4c è valido sia per il JFET che per il MOSFET,

Lunica differenza sta nei diversi valori che gm e go assumono nei due dispositivi.

Calcoliamoli:

VALORE DI gm E DI gO PER IL JFET

Calcoliamo i valori di gm e di go per il NJFET , per il calcolo del PJFET si procede allo stesso modo.

sappiamo che ID

iD = IDSS (1-VGS/VP)2 (1+λVDS);

sappiamo che

gm = δiD/δvGS)

derivando l'espressione rossa rispetto a vGS si ottiene:

gm = 2ID/vGS- vP

sappiamo inoltre che

go = (δ iD/δvDS)

derivando l'espressione rossa rispetto a vDS si ottiene:

go = (ID/(1+λVDS) ) λ = λID

VALORE DI gm E DI gO PER IL MOSFET

Calcoliamo i valori di gm e di go per il NMOSFET , per il calcolo del PMOSFET si procede allo stesso modo.

sappiamo che ID

ID = K/2 (VGS - VT)2(1+λVDS)

sappiamo che

gm = δiD/δvGS)

derivando l'espressione rossa rispetto a vGS si ottiene:

gm = 2ID/vGS- vT

sappiamo inoltre che

go = (δ iD/δvDS)

derivando l'espressione rossa rispetto a vDS si ottiene:

go = (ID/(1+λVDS) ) λ = λID

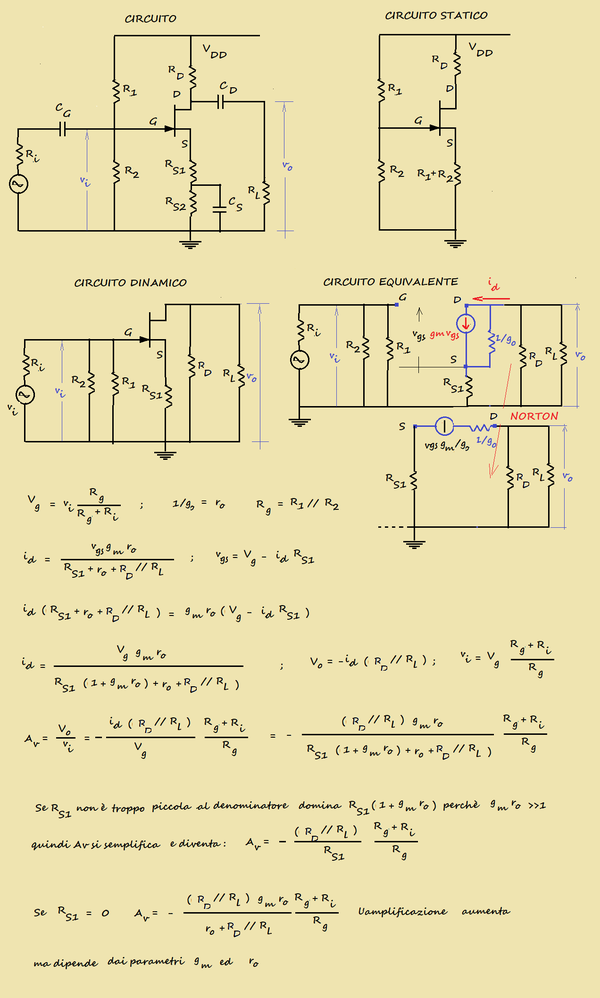

FET COME AMPLIFICATORE

In fig.5a parte sinistra è rappresentato il circuito dinamico nel quale, rispetto a quello statico di fig.5 i generatori di tensione continua sono considerati dei cortocircuiti.

Ricordando quanto detto in precedenza il circuito equivalente del circuito dinamico è quello riportato in fig.5 parte destra.

CONFIGURAZIONI AMPLIFICATRICI DEL FET

SOURSE COMUNE

L'ingresso è fra il Gate ed il Sourse e l'uscita fra il Drain ed il Sourse; il terminale Sourse è in comune.

Facendo riferimento alla fig.5b dal circuito si passa al circuito statico poiché in continua i condensatori equivalgono ad un circuito aperto; dal circuito si passa al circuito dinamico poiché in alternata i condensatori e i generatori in continua equivalgono ad un corto circuito.

Le circuito equivalente del piccolo segnale ne abbiamo parlato in precedenza.

AMPLIFICAZIONE A VUOTO, RESISTENZA D'INGRESSO, RESISTENZA D'USCITA

DRAIN COMUNE

L'ingresso è fra il Gate ed il Drain e l'uscita fra il Sourse ed il Drain ; il terminale Drain è in comune.

Facendo riferimento alla fig.6 dal circuito si passa al circuito statico poiché in continua i condensatori equivalgono ad un circuito aperto; dal circuito si passa al circuito dinamico poiché in alternata i condensatori e i generatori in continua equivalgono ad un corto circuito.

GATE COMUNE

L'ingresso è fra il Sourse ed il Gate e l'uscita fra il Drain ed il Gate ; il terminale Gate è in comune.

Facendo riferimento alla fig.7 dal circuito si passa al circuito statico poiché in continua i condensatori equivalgono ad un circuito aperto; dal circuito si passa al circuito dinamico poiché in alternata i condensatori e i generatori in continua equivalgono ad un corto circuito

gm /go = μ

vi = μVgs / (1+μ)

vo= μVgs (RD//RL) / (1/go + (RD//RL) )

Av = vo/vi = (1+μ) (RD//RL) / (1/go + (RD//RL) )

Ri= RD// (1/go + (RD//RL) )/(1+μ

Ro = RD// (1/go + (RS//Rs)(1+μ) )

L'amplificazione è alta la resistenza di ingresso è bassa la resistenza d'uscita è media.

VALORI DI Av , Rin ed Rout VELLE VARIE CONFIGURAZIONI DI AMPLIFICAZIONE

La Fenice rinasce dalle proprie ceneri

Il tuo sito senza pubblicità?

Puoi con JimdoPro e JimdoBusiness!

La dritta